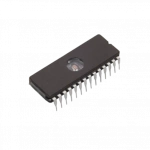

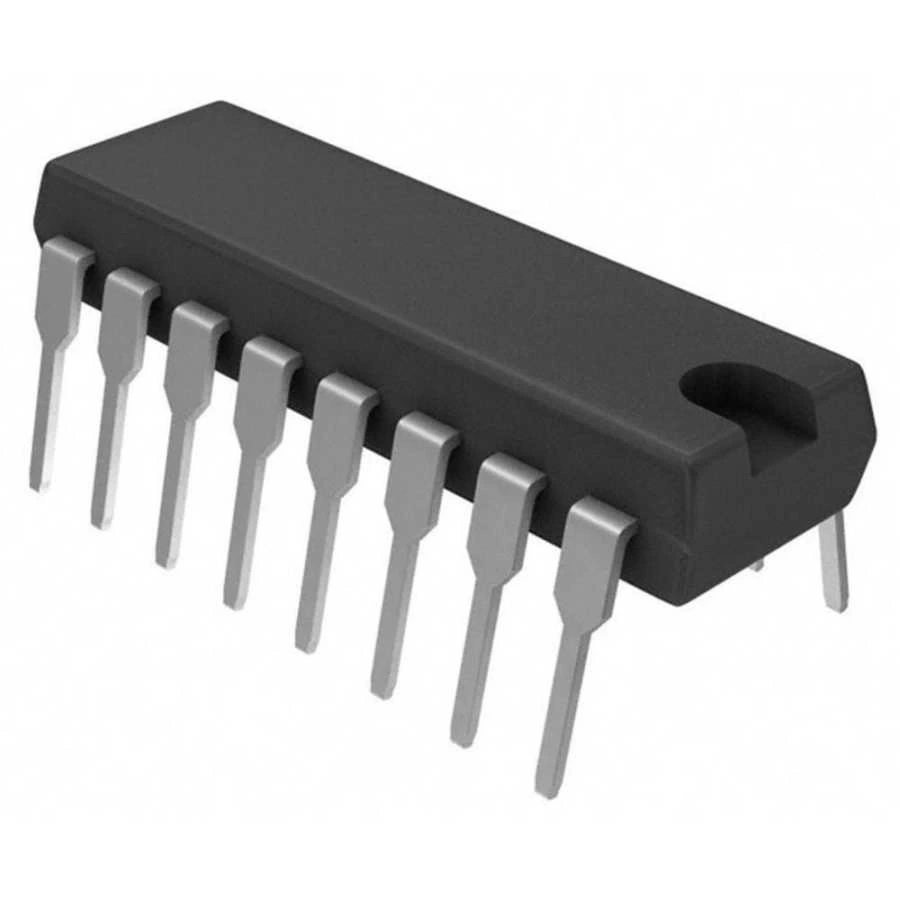

CD4027 DIP-16 Flip Flop Entegresi

CD4027, çift J-K pozitif kenar tetiklemeli flip flop entegresidir. DIP-16 paketinde sunulan bu entegre, CMOS teknolojisi ile üretilmiş olup, düşük güç tüketimi ve yüksek gürültü bağışıklığı özelliklerine sahiptir.

Her bir flip flop için J, K, set, reset ve clock girişleri ile Q ve Q? çıkışlarına sahip olan CD4027, dijital durum saklama, sayaç ve zamanlama uygulamaları için idealdir. Elektronik komponentler arasında dijital devre tasarımlarında sıkça kullanılır.

Geniş besleme voltajı aralığında çalışabilen bu entegre, entegreler içinde güvenilir bir seçenektir. Flip flop entegresi olarak esnek kontrol olanakları ve J-K tipi çalışma modları ile geniş kullanım alanı sunar.

Teknik Özellikler

CD4027 DIP-16 Flip Flop Entegresi'nin detaylı teknik özellikleri aşağıda listelenmiştir.

- Entegre Tipi: Çift J-K Pozitif Kenar Tetiklemeli Flip Flop

- Üretici: Texas Instruments / NXP / ST Microelectronics

- Paket Tipi: DIP-16

- Besleme Voltajı Aralığı: 3.0V - 18.0V

- Önerilen Çalışma Voltajı: 5.0V - 15.0V

- Teknoloji: CMOS

- Flip Flop Sayısı: 2

- Flip Flop Tipi: J-K

- Tetikleme Tipi: Pozitif Kenar (Rising Edge)

- Giriş Sayısı (Her Flip Flop): 5 (J, K, CLK, SET, RESET)

- Çıkış Sayısı (Her Flip Flop): 2 (Q, Q?)

- Maksimum Çalışma Frekansı: 8MHz (tipik, VDD=10V)

- Propagasyon Gecikmesi: 90ns (tipik, VDD=10V)

- Çıkış Akımı (Kaynak): -0.88mA (tipik, VDD=10V)

- Çıkış Akımı (Havuz): 0.88mA (tipik, VDD=10V)

- Güç Tüketimi: 0.2μW (tipik, statik, VDD=5V)

- Fan-Out (4000B Serisi): 50 yük

- Giriş Kapasitansı: 5pF (tipik)

- Çıkış Kapasitansı: 7pF (tipik)

- Çalışma Sıcaklığı: -55°C ile +125°C arası

- Lojik Seviyeler: CMOS uyumlu

- Pin Sayısı: 16

- Montaj Tipi: Through-Hole (Delikli Montaj)

- RoHS Uyumluluğu: Evet

Kullanım Alanları

CD4027 DIP-16 Flip Flop Entegresi'nin kullanılabileceği çeşitli alanlar ve uygulama örnekleri.

Sayaç ve Zamanlayıcı Devreleri

- İkili sayaçlar

- Frekans bölücüler

- Zaman geciktirme devreleri

- Darbe genişlik modülatörleri

- Kare dalga osilatörleri

Dijital Kontrol Sistemleri

- Durum makineleri

- Kontrol mantığı

- Anahtar debounce devresi

- Tuş kilitleme devresi

- Mode seçme devreleri

Veri İşleme

- Veri yakalama ve tutma

- Senkronizasyon devreleri

- Kenar algılama

- Seri-paralel dönüşüm

- Toggle anahtarlama

Avantajlar ve Özellikler

CD4027 DIP-16 Flip Flop Entegresi'nin sağladığı avantajlar ve çözümler.

- J-K Flip Flop Yapısı: Esnek çalışma modları (Set, Reset, Toggle)

- Çift Flip Flop: Tek pakette iki bağımsız J-K flip flop

- Asenkron Kontrol: Set ve Reset girişleri ile doğrudan kontrol imkanı

- Düşük Güç Tüketimi: CMOS teknolojisi ile minimum enerji kullanımı

- Geniş Besleme Aralığı: 3V-18V arası çalışabilme

- Komplementer Çıkışlar: Hem Q hem de Q? çıkışı

- Gürültü Bağışıklığı: CMOS yapısı ile yüksek gürültü toleransı

- Toggle Modu: J=1, K=1 durumunda otomatik toggle işlemi

- Endüstri Standardı: Yaygın olarak desteklenen entegre

- Yüksek Fan-Out: Çok sayıda CMOS giriş sürebilme

Devre Tasarımı ve Kullanım

CD4027 DIP-16 Flip Flop Entegresi'nin devre tasarımında kullanımı hakkında bilgiler.

İpucu: Kullanılmayan girişleri asla açık bırakmayın, SET ve RESET girişlerini VDD'ye, J ve K girişlerini VSS'ye bağlayın.

Pin Yapılandırması (DIP-16):

- Pin 1: Q? (1. Flip Flop Q Çıkışı)

- Pin 2: Q?? (1. Flip Flop Q? Çıkışı)

- Pin 3: CLK? (1. Flip Flop Clock Girişi)

- Pin 4: RST? (1. Flip Flop Reset, Aktif Yüksek)

- Pin 5: SET? (1. Flip Flop Set, Aktif Yüksek)

- Pin 6: K? (1. Flip Flop K Girişi)

- Pin 7: J? (1. Flip Flop J Girişi)

- Pin 8: VSS (Toprak)

- Pin 9: J? (2. Flip Flop J Girişi)

- Pin 10: K? (2. Flip Flop K Girişi)

- Pin 11: SET? (2. Flip Flop Set, Aktif Yüksek)

- Pin 12: RST? (2. Flip Flop Reset, Aktif Yüksek)

- Pin 13: CLK? (2. Flip Flop Clock Girişi)

- Pin 14: Q?? (2. Flip Flop Q? Çıkışı)

- Pin 15: Q? (2. Flip Flop Q Çıkışı)

- Pin 16: VDD (Pozitif Besleme)

Temel Bağlantı Şeması:

- VDD (Pin 16) pozitif besleme voltajına (3V-18V) bağlanır

- VSS (Pin 8) toprak hattına bağlanır

- VDD ve VSS arasına 0.1μF bypass kapasitörü bağlanır

- J ve K girişleri (Pin 7, 6, 9, 10) kontrol sinyallerine bağlanır

- CLK girişleri (Pin 3, 13) saat sinyaline bağlanır

- SET girişleri (Pin 5, 11) normal çalışma için VSS'ye, set için VDD'ye bağlanır

- RST girişleri (Pin 4, 12) normal çalışma için VSS'ye, reset için VDD'ye bağlanır

- Q ve Q? çıkışları (Pin 1, 2, 15, 14) kontrol edilecek devrelere bağlanır

J-K Flip Flop Çalışma Tablosu:

- J=0, K=0, CLK=↑: Durum korunur (Q değişmez)

- J=0, K=1, CLK=↑: Reset (Q=0, Q?=1)

- J=1, K=0, CLK=↑: Set (Q=1, Q?=0)

- J=1, K=1, CLK=↑: Toggle (Q değişir, Q? değişir)

- SET=1: Q=1, Q?=0 (Clock'tan bağımsız)

- RST=1: Q=0, Q?=1 (Clock'tan bağımsız)

- SET=1, RST=1: Belirsiz durum (kullanılmamalı)

Uygulama Örnekleri:

- İkiye Bölücü: J=1, K=1 olarak ayarlanıp clock kenarlarında toggle yaparak frekans bölme

- T Flip Flop: J ve K pinlerini birbirine bağlayarak (J=K)

- D Flip Flop: J'ye veri, K'ya verinin tersi bağlanarak (K=J?)

- Darbe Yakalama: Reset ile temizlenen, J=1 durumunda darbe yakalayan devre

- 4-Bit Sayaç: Dört flip flop kaskad bağlanarak ve her birinin Q çıkışı sonrakinin CLK girişine bağlanarak

Sorun Giderme ve İpuçları

CD4027 DIP-16 Flip Flop Entegresi kullanırken karşılaşabileceğiniz sorunlar ve çözüm önerileri.

Yaygın Sorunlar ve Çözümleri

- Tetikleme Sorunları: CLK sinyalinin yükselme zamanı çok yavaş olabilir, daha hızlı yükselme zamanı sağlayın

- Kararsız Çalışma: Bypass kapasitörlerini ve besleme voltajını kontrol edin

- Toggle Çalışmıyor: J ve K girişlerinin her ikisinin de lojik 1 olduğunu kontrol edin

- Durum Değişimleri: SET ve RST pinlerinin normalde lojik 0 olduğunu kontrol edin

- Giriş Dalgalanması: Giriş pinlerine pull-up/pull-down dirençleri ekleyin

CMOS Önlemleri

- CMOS entegrelerin statik elektrik hasarına karşı duyarlı olduğunu unutmayın

- Antistatik önlemler alın ve entegre ile çalışırken topraklama bileziği kullanın

- Besleme voltajını uygun sınırlar içinde tutun

- Giriş pinlerinde lojik seviyenin VDD'yi aşmamasına dikkat edin

- Boşta kalan girişleri daima belirli bir lojik seviyeye bağlayın

Frekans ve Zamanlama İpuçları

- Yüksek frekanslı uygulamalarda hat kapasitanslarını minimize edin

- Uygun çıkış yüklemesi için fan-out sınırını aşmayın

- Clock kenarlarının temiz ve gürültüsüz olmasını sağlayın

- Besleme hattına birden fazla bypass kapasitörü ekleyin (0.1μF ve 10μF)

- Toggle modunda maksimum frekansın besleme voltajına bağlı olduğunu unutmayın

Paket İçeriği

İlgili Ürün Kategorilerimiz

Çeşitli elektronik komponentler ile projelerinizi ve devrelerinizi geliştirebilirsiniz.

Ürünleri İncele →Geniş entegre çeşitleri ile elektronik projelerinize fonksiyonellik kazandırabilirsiniz.

Ürünleri İncele →Flip flop entegreleriyle dijital durum saklama ve senkronizasyon projelerinizi gerçekleştirebilirsiniz.

Ürünleri İncele →

Neden Voltaj.Net'ten Almalısınız?

Voltaj.Net, elektronik komponentler ve entegreler konusunda Türkiye'nin güvenilir tedarikçisidir.

- Kalite Güvencesi: Orijinal ve güvenilir ürünler

- Teknik Destek: Uzman ekip ile çözüm ve danışmanlık

- Teslimat: Stoktan hızlı gönderim imkanı

- Geniş Ürün Yelpazesi: Projeleriniz için gerekli tüm komponentler

- Uygun Fiyatlar: Rekabetçi fiyatlarla kaliteli ürünler

- Güvenilir Alışveriş: Kolay sipariş ve güvenli ödeme seçenekleri

Ürün Hakkında Sıkça Sorulan Sorular

CD4027 ve 74HC76 arasındaki fark nedir?

CD4027 CMOS teknolojisi, 74HC76 yüksek hızlı CMOS teknolojisi kullanır. CD4027 3-18V arasında çalışır, 74HC76 2-6V arasında çalışır. İkisi de J-K flip flop içerir.

J-K flip flop'un D flip flop'tan farkı nedir?

J-K flip flop daha esnek çalışma modları sunar. J=K=1 durumunda toggle (çıkışın tersi) moduna geçer. D flip flop ise sadece D girişindeki veriyi aktarır.

Entegre kaç MHz'e kadar çalışabilir?

Besleme voltajına bağlıdır. 5V'ta yaklaşık 4MHz, 10V'ta 8MHz, 15V'ta 10MHz civarında çalışabilir. Devrenin kapasitif yükü de frekansı etkiler.

Toggle modu (J=K=1) için ne tür uygulamalar yapılabilir?

Frekans bölücü, sayaç devreleri, ikili LED flaşör ve kare dalga osilatörü gibi uygulamalar yapılabilir. Her clock darbesinde çıkış durumu değişir.

SET ve RESET pinleri nasıl kullanılır?

SET=1 yapıldığında Q=1 olur. RESET=1 yapıldığında Q=0 olur. Bu işlemler CLK'dan bağımsızdır ve asenkron kontrol sağlar. Normal çalışmada LOW tutulmalıdır.

CD4027 ile 4-bit sayaç nasıl yapılır?

İki adet CD4027 kullanılır. Tüm flip floplar için J ve K girişleri HIGH yapılır. Her flip flopun Q çıkışı sonraki flip flopun CLK girişine bağlanır.

Kullanılmayan girişler nasıl bağlanmalıdır?

SET ve RESET girişleri VSS'ye (LOW), J ve K girişleri VSS'ye (LOW) veya VDD'ye (HIGH) bağlanmalıdır. Asla açık bırakılmamalıdır.

CD4027 ile kare dalga üreteci nasıl yapılır?

J ve K girişlerini HIGH yapın. Çıkışlardan birini bir RC devresi üzerinden kendi CLK girişine bağlayın. Frekans RC değerleriyle belirlenir.